Virtuoso ADE Verifier

模拟规格验证工具

主要优点

-

能够验证模拟电路

-

综合考虑一系列重要的设计参数

-

符合底层指标测试的高级设计要求

-

TÜV SÜD“符合目标 – TCL1”经认证符合ISO 26262汽车功能安全要求

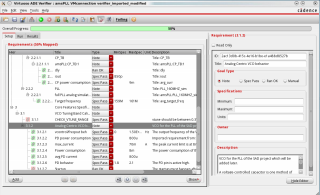

Cadence® Virtuoso® ADE Verifier的设计初衷是为电路状态提供全局性视角。Virtuoso ADE product suite中的Virtuoso ADE Verifier联合Virtuoso ADE Assembler和Virtuoso ADE Explorer,使创建于这些环境下的测试能够对接最高级的设计要求。

Virtuoso ADE Verifier将单个规格测量测试,和功耗、增益以及带宽等等高级的指标要求链接在一起。

Virtuoso ADE Verifier可实现团队中多位设计师或不同地区的规格测量测试的整合,并且能够通过一个易于读取的窗口显示通过/失败状态。The Virtuoso ADE Verifier还能够快速确定尚未分配测量的要求,如果特定测量所连接的测试太少,它还能够提供视觉线索。

模拟设计规划流程

借助Virtuoso ADE Verifier,您可以测试并确保设计符合您的标准。这一工具有助于关键路径电路模块达到规范要求,确保同一设计的所有功能块符合这一标准。通常,设计目标在项目周期的早期阶段即已确定,然后分配给各位工程师,用于资料记录和测试。

Virtuoso ADE Verifier将初始设计规范与结果相结合,能够尽早发现特定电路中可能出现的问题。

Virtuoso ADE Verifier将初始设计规范与结果相结合,能够尽早发现特定电路中可能出现的问题。

模拟设计整合流程

Virtuoso ADE Verifier可在创建单个测试后,建立高级的规范层级。如设计由多位Virtuoso平台外的独立工程师合作完成,您可以对此加以利用。Virtuoso ADE Verifier将各部分重新组合成一个全面集成的驾驶舱,便于确定测试是否过时、缺失或不符合设计目标。

作业监控

Virtuoso ADE Verifier能够通过图形用户界面或使用命令行脚本运行仿真作业。这些仿真作业能够通过一个作业监控窗口启动,窗口中显示了测试进程,而架构师可通过这些仿真作业了解是否存在任何运行故障需要进一步的调查。

与MathWorks MATLAB集成

与MathWorks MATLAB的集成使您能够在验证定制、射频和混合信号设计时加快大型数据集的处理。

-

平台之间无缝共享数据,允许数据挖掘和高效分析,从而缩短上市时间

-

使用专家级编码知识和底层应用程序接口解决复杂的数据计算

ISO 26262汽车TCL1认证

业界首个模拟/混合信号设计实现和验证流程,旨在实现“符合目的-一级软件工具信赖水平(TCL1)”认证,使您能够满足严格的ISO 26262汽车安全要求。 该流程使用Virtuoso ADE Product Suite和Spectre® Circuit Simulation Platform,从创建和仿真到物理实现和验证,实现晶体管级设计。Virtuoso ADE Verifier为设计工程师提供了一种集成的方法,可以根据单个电路规范验证安全规范,以提升设计信心。有关安全手册、工具信度分析(TCA)文件和TÜV SÜD公司合规报告的信息,请通过Cadence在线支持下载功能安全文件包。