Virtuoso Layout Suite EAD

通过实时反馈避免多次设计迭代

主要优势

-

在版图创建时,利用内置的互连寄生抽取引擎对其进行即时评估,从而执行实时分析和优化

-

使您能够设置电气约束,并实时观察是否满足这些约束

-

提醒您注意绘制版图时产生的电迁移问题

-

针对现有互连寄生参数对部分版图进行重新仿真,最大限度地减少重新设计和“过度设计”

-

缩短电路设计周期多达30%

-

使您能够优化芯片性能并优化面积

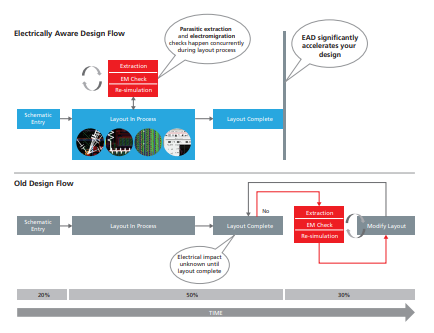

Cadence® Virtuoso® Layout Suite for Electrically Aware Design (EAD)具有独特的设计阶段电气验证功能,可提高设计团队的生产率和定制IC的电路性能。

借助Virtuoso Layout Suite EAD,您将掌握如何避免多次设计迭代和“过度设计”的技术和方法您将能够在创建版图时监控电气问题,并对互连决策进行实时的电分析、仿真和验证。 因此,您将能够实现自动建构校正版图。 该解决方案中独特的设计阶段验证功能使您的电路设计周期缩短达30%,并在更小面积内实现更佳的芯片性能。

借助Virtuoso Layout Suite EAD,您可以节省几天到几周的设计时间。该解决方案实时抽取互连寄生参数,并适用于部分设计。版图和电路设计人员将能够更有效地协作,对电气问题的实时可视性也得以提高。该解决方案能够与Virtuoso平台中的其它工具无缝配合,如此一来,您将能够从Virtuoso Analog Design Environment中运行的仿真中获取电流和电压,并将这些电气信息传递到版图环境中。

Virtuoso Layout Suite EAD 编辑