Custom/Analog Advanced Node

Innovative capabilities for custom/analog designs at 20nm and below

主要好处:

-

提高硅的质量:从头进行重新设计,以支持最激进的高级节点工艺

-

提高生产率:新的设计方法以及针对性的自动化技术的引入极大地提高了电路设计师和布局工程师的生产率。与传统的设计工具和流程相比,利用这些流程和技术可以使您的生产率提高多达5倍。

-

准确地预测和管理可变性:与领先的代工厂紧密合作可在Virtuoso®高级节点平台内提供功能,使您能够在设计流程中预先预测和管理可变性,并避免由于工艺可变性而导致的昂贵设计重制。

-

高级节点定制设计的行业领导者:Virtuoso高级节点平台支持并通过所有主要的高级20/16/14/10 / 7nm技术认证

用于20nm及以下波长的定制/模拟设计的创新功能

有据可查的是,在高级流程节点上进行设计是极其复杂且昂贵的。考虑到这一点,片上系统(SoC)解决方案必须具有正确的特性、功能和性能组合,以证明在这些节点上进行设计是合理的。但是定制/模拟设计师最关心的是制造复杂性带来的挑战。Cadence公司®的Virtuoso先进节点平台具有创新的功能集,使设计人员能够充分利用硅的这些工艺节点。

避免密度梯度效应

在20nm,16nm,10nm,7nm高级工艺节点上进行设计

在20nm / 16nm / 14nm / 10nm / 7nm先进节点上进行设计的独特之处在于,除了不断增加的功率和性能规格外,制造和可变性之间的深层,复杂的相互依赖性。

问题包括:

- 多重图案技术(MPT)和色彩感知的物理设计,包括双重,三重,四重和五重图案

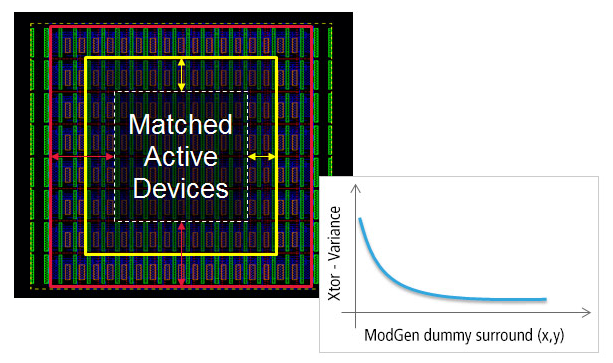

- 依赖于布局的效果(LDE)和密度梯度效果(DGE),其中布局上下文(放置在靠近设备的位置)可能会影响设备性能多达30%

- 先进的颜色感知自定义路由

- 物理设计规则呈指数增长

- 设备变化和灵敏度

- 新型晶体管(例如,FinFET)

避免EM违规

Virtuoso高级节点平台

Virtuoso先进节点平台改进了单点工具以应对这些挑战,并启用了新的设计方法,可实现快速的布局原型设计,设计中的签收以及原理图和布局设计者之间的紧密协作,这对于在高级设计人员中进行高效设计至关重要的过程节点。

Virtuoso高级节点平台的最新版本包括:

- 对基于FinFET的设计的强大支持,要求MPT管理电路设计上的器件可变性和灵敏度

- 许多增强的交互式和自动化功能,以支持结构化布局方法,包括核心编辑命令,交互式电线编辑器,模块生成器(ModGens),全自动定制布线和辅助放置,所有设计规则检查(DRC)和正确上色的功能

- 与Virtuoso物理验证系统(PVS)的独特紧密结合,在Virtuoso Layout Suite中为DRC和颜色分解启用签收验证支持

多图案支持和色彩感知的物理设计

设计中设计规则检查