Sigrity OptimizePI

优化执行实现低成本高性能

核心优势

-

自动选择和放置去耦电容

-

以最低的去耦电容成本满足供电系统需求

-

重新获取被不必要的去耦电容占据的有效设计区域

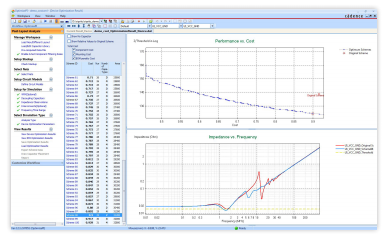

Cadence® Sigrity™ OptimizePI™ 技术可实现针对电路板和IC封装的完整交流频率分析,确保您的设计在系统级和器件级拥有高性能表现,同时为您节省15%至50%的去耦电容成本。 支持预布局和布局、布线后研究,不仅能够满足您的供电网络(PDN)需求,更能以最低的成本快速确定最佳的去耦电容选择和放置位置,使您的设计得到最优化。

Sigrity OptimizePI技术建立在成熟的Cadence混合电磁电路分析技术基础之上,并结合独特的Sigrity优化引擎,帮助您快速定位最佳去耦电容选择和放置位置。

主要功能

-

避免PCB和IC封装的去耦电容过度设计

-

降低新设计和后期制作产品的PDN成本

-

为封装器件制定有效的去耦电容指南

-

优化电路板/ IC封装接口的PDN

-

识别EMI 去耦电容的数量和位置

-

强大且成熟的混合EM/ 电路分析技术

-

直观的、可交互的PDN性能可视化界面

-

轻松设置预布局和布局、布线后的去耦电容优化

-

使用Cadence Allegro® PowerTree™ 数据,可视化原理图的电源部分

-

在PowerTree 用户界面中获取设置信息(模型、网络名称等)、分配目标阻抗约束

-

独特的器件阻抗检查和EMI谐振检查

-

可支持包含封装和电路板数据的大型设计

-

支持Mentor、Zuken和Altium接口,允许混合CAD数据库,满足多结构设计