Virtuoso System Design Platform

Unified “system-aware” platform for IC and

package design

package design

主要好处

-

使工程师能够跨芯片,封装和电路板同时设计,从而节省时间并最大程度地减少错误

-

集成多个异构IC的设计的理想选择,包括RF,模拟和数字设备

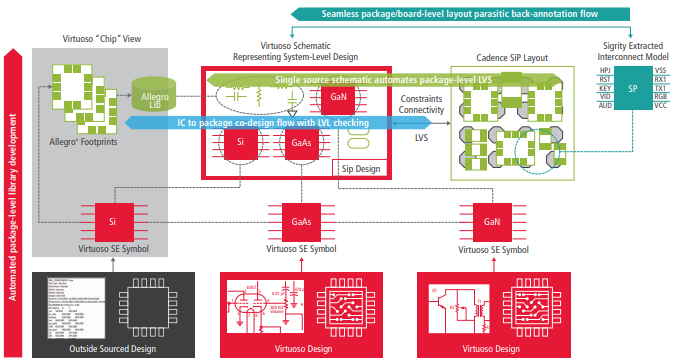

Cadence公司® 的Virtuoso ® 系统设计平台连接两个世界级的Cadence技术,定制IC设计和封装/ PCB设计/分析,建立一个全面的方法,它自动化并简化多模异构系统的设计和验证流程。

利用 Virtuoso原理图编辑器 和 Virtuoso模拟设计环境,它为IC和封装/系统级的设计捕获,分析和验证提供了一个平台。此外,炫技化系统设计平台提供了与Cadence公司的SiP级实现环境和自动双向接口 Sigrity公司™ PowerSI ® 3DEM提取选项。

Virtuoso系统设计平台使IC设计人员可以轻松地在IC验证流程中包含系统级布局寄生虫,从而通过将封装/电路板布局连接性数据与IC布局寄生电气模型相结合来节省时间。自动生成的“系统感知”原理图,其结果可轻松用于创建用于最终电路级仿真的测试平台。Virtuoso系统设计平台使整个流程自动化,从而消除了将系统级布局寄生模型重新集成到IC设计人员流程中的高度手动且容易出错的过程。

集成异构设备

当今的许多模拟,RF和混合信号设计都需要在不同的基板技术上集成多个IC,以实现所需的性能目标。异构器件的集成使设计人员可以获得使用单片IC(SoC)设计方法无法轻松复制的结果。同时,异构集成为当今的设计师带来了全新的挑战。

封装系统(SiP)是将混合技术集成到单个设计中的最常用方法之一。这种方法需要IC与封装基板设计团队之间的无缝集成,以及集成的工具流程。Virtuoso系统设计平台通过一种新颖的跨平台解决方案来应对这些挑战,该解决方案可简化和自动化具有片外设备和基于不同工艺设计套件(PDK)的多个IC的封装/模块的设计。

Virtuoso系统设计平台流程

特征

- 单个分层原理图通过封装级逻辑捕获IC,从而实现了自动化的布局-示意图(LVS)验证流程

- IC验证方法无缝地生成可用于测试台的原理图,这些原理图包括系统级布局寄生数据,从而消除了电子签核的猜测

- 封装级无源器件的内置,准确,快速的3D EM建模,可进一步简化IC验证流程

- 强大而灵活的实施技术,支持所有类型的高级包装技术