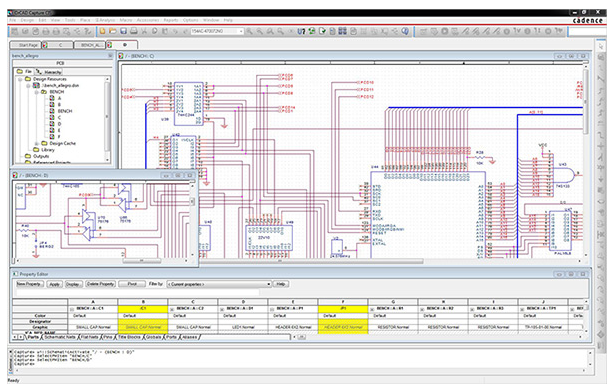

Allegro Design Entry Capture/Capture CIS

Fast and intuitive schematic design entry

主要好处

-

通过分层和变型设计功能提高复杂设计的原理图编辑效率

-

强大的CIS可以推广首选的当前零件,以加快设计过程并降低项目成本

-

TÜV南德意志集团“专用于TCL1”认证,符合ISO 26262汽车功能安全要求

易于使用和功能强大,Cadence公司®快板®设计输入采集和捕获组件信息系统(CIS)是使用最广泛的原理图设计的解决方案,同时支持平板和从最简单到最复杂的层次化设计。与Allegro PCB的无缝双向集成可实现原理图与电路板设计之间的数据同步和交叉探测/放置。Allegro Design Entry Capture和Capture CIS允许设计人员使用反馈过程来对布局更改进行反注释,进行栅极/引脚交换,以及将组件名称或值从电路板设计更改为原理图。它还带有大量的原理图符号库,并且可以多种格式导出网表。

Allegro Design Entry Capture和Capture CIS将原理图设计应用程序与CIS的附加功能集成在一起。CIS允许设计人员搜索,识别和填充带有首选零件的设计。通过轻松访问公司零件数据库和零件信息,设计人员可以减少研究所需零件所花费的时间。

汽车TCL1获得ISO 26262认证

业界首个获得“针对用途-工具信心等级1(TCL1)”认证的PCB设计和验证流程,使您能够满足严格的ISO 26262汽车安全要求。该流程包括使用PSpice的一切,从设计,制作到模拟物理实现和验证®,快板,和的OrCAD ® 产品套件。高性能的设计输入,仿真和布局编辑工具为设计工程师提供了一个集成的环境,使他们可以针对各个电路规范来验证安全规范,以增强设计信心。有关安全手册,工具可信度分析(TCA)文档以及TÜVSÜD的合规性报告的信息,请下载功能安全文档套件。 通过Cadence在线支持。

Allegro设计输入捕捉和Capture CIS为使用PSpice进行PCB开发或模拟仿真提供了快速直观的原理图设计输入