Interface-Aware Approach

Hierarchical approach to accelerate PCB design authoring and implementation

主要好处

-

设计创作和实施速度提高15%

-

以更高的抽象水平设计PCB

-

更快地路由基于标准的接口,包括DDR3,DDR4,SATA和PCIe

如果你是一个系统设计师,你很可能转向协议如的DDRx和PCI Express ® (的PCIe ®),以支持性能,功耗和带宽的您的产品的需求。您的设计创作和布局工具是否提供了与设计周期要求保持同步所需的速度和易用性?如果您可以应用分层接口感知方法来加快PCB设计创作和实施过程,并一路提高设计质量,性能和可靠性,该怎么办?

好了,现在你可以用Cadence公司® 快板® PCB设计流程,最新版本(16.65)已得到增强,界面感知的设计能力。结果?将设计创作和实施速度提高多达15%。该功能使您可以在更高的抽象水平上设计PCB,从而可以更快地路由基于标准的接口,包括DDR3,DDR4,串行ATA(SATA)和PCIe。

支持当今的高速接口

让我们看一下接口感知设计功能的工作方式。传统的设计创作工具可以处理总线或捆绑以及一组信号的单级分层定义。但是,当今的接口无法在单级层次结构中建模。要解决的其他挑战包括约束数量的增加,设计密度的增加,引脚间距的减小以及大型引脚数器件的数量的增加以及布线设计的时间增加(面对缩短的设计周期和资源)。

为了快速,轻松地连接接口,Allegro PCB设计流程中的分层接口感知设计功能:

-

使创作在更高的抽象水平上得以提高生产力

-

将接口定义传递给布局设计器

-

指导关键零部件的放置并进行路线规划

-

允许您使用自动交互技术来进一步加速接口的中断,路由和调整

借助集成的功能,Allegro Design Entry HDL中的PCB原理图创作技术可以在原理图中使用新的图形对象,从而可以实例化接口和分层网络组,配置并将接口连接到组件和模块,以及将接口应用于组件。

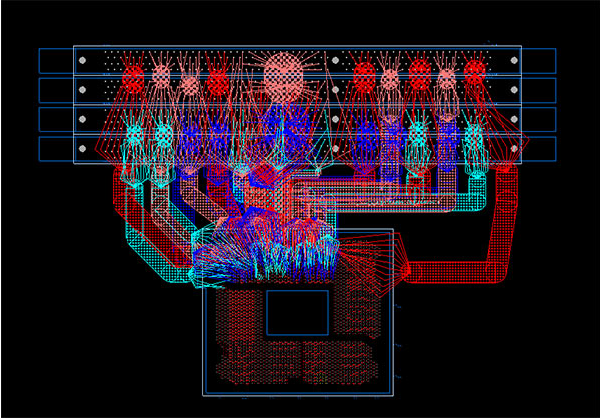

可视化DDR3接口的分层路由规划

由于该功能支持多个层次结构,因此将约束应用于以逻辑方式分组的信号变得更加容易。具有接口感知功能的Allegro工具(Allegro设计创作,Allegro约束管理器和Allegro PCB编辑器)可在设计画布上自动创建并可视地标识网络组。这些工具还可以“嵌套”网络组以包括包含字节通道的子组。您将能够可视化界面的整个物理域,以查看不适当的部分。通过网络组的颜色编码,您可以轻松地确定有问题的区域并应用适当的层分布。

具有接口意识的设计功能为您提供了一种可视化接口总体路由域的方法,因此您可以查看哪些部分不正确

概要

凭借Allegro PCB设计流程中可用的分层接口感知设计能力,路由高速接口(例如DDRx和PCIe)变得更快,更直接。该功能支持更高抽象级别的PCB设计,在提供视觉位置指示的同时加快了设计创作和实施的速度,并使您能够在设计周期的早期识别出布线问题。