DDR4 Power-Aware Signal Integrity

DDR4 Power-Aware Signal Integrity Adopting Serial Link Simulation Techniques

信号完整性(SI)先知曾预言这次会到来,事实证明他们是对的。SI工程师在过去十年中一直在使用这种技术来分析多千兆位串行链路接口,现在已开始将其应用于并行存储器接口,例如DDR4。这一切都说得通。

当PCI Express最初以2.5Gbps的速度出现时,我们看到了进行仿真和分析的方式发生了巨大的变化,从而永远改变了SI格局。评估从10,000位以上的巨大位流得出的眼图的要求将传统电路仿真推向了表征角色,并且基于卷积的通道仿真器应运而生,以应对新的大容量仿真需求。为了有效地对包括实时自适应在内的均衡效果进行建模的需求,产生了可执行的“算法”模型,并且针对“算法建模接口”的称为“ AMI”的新功能被引入了行业标准的IBIS规范中。那是SI世界中令人振奋的时刻)。

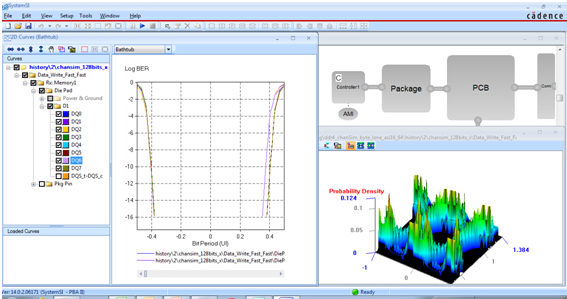

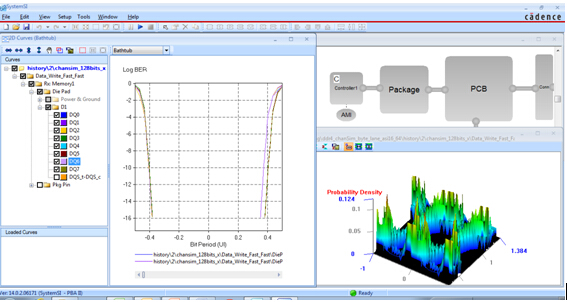

串行链接分析技术,例如带有浴盆曲线的误码率(BER),大容量仿真和眼图,现在已成为内存接口分析的一部分

串行链接分析技术,例如带有浴盆曲线的误码率(BER),大容量仿真和眼图,现在已成为内存接口分析的一部分现在,我们已迈入了一个新时代,我们今天处理的内存接口看起来异常“串行链接”。今天我们看到的DDR4数据总线的数据速率恰好是我们最初使用PCI Express的速率。DDR4 I / O结构与我们过去在SerDes空间中的结构相似,具有内置的上拉上拉终端,以及良好的线性,对称,性能良好的输出阻抗。尽管信号仍然是单端的,但数据总线已朝着点对点的拓扑靠拢,在可能的情况下,更多地使用PCB顶部和底部的“翻盖式”组件放置来将负载集中在传输线的末端。尽管均衡化仍没有现成的存储设备(主要是出于成本原因)。

除了具有串行链路特性之外,用于分析DDR4的技术也正在向传统用于串行链路的技术转变。DDR4的数据总线合规性和时序已从传统的逐周期设置和保持标准转变为基于掩码的合规性,这是SerDes设备和串行链路常用的。而且,DDR4 JEDEC规范现在指定了目标BER;“设计规范是BER <1e-16……如果需要,可以使用双重狄拉克方法对BER进行表征和推断……”这些类型的规范与串行链路接口已经使用了多年。

那么所有这些将我们引向何方?Cadence Sigrity SystemSI-并行总线分析已将串行链路通道仿真引擎集成到其中,并成功地将其应用于耦合的单端并行总线,甚至包括非理想的功率效应(正在申请专利)。这给我们带来了什么?首先,它为我们带来了仿真能力,因此您现在具有通过存储器接口运行数十万甚至数百万位流量的独特能力,远远超出了传统电路仿真的能力。这样,当您在示波器上采样许多非常有价值的数据时,就可以看到眼睛在实验室中的真实样子。这还可以注入确定性和随机抖动,因此您可以看到对眼睛有什么影响。

AMI建模也随之而来。引入通道仿真后,您还可以自由使用AMI模型进行控制器上使用的均衡。可以直接利用与串行链接应用程序一起使用的FFE建模进行控制器均衡,并且Sigrity SystemSI包含全面的AMI模型。

但是从根本上讲,所有这些仿真功能和建模功能都可以生成非常详细的眼图分布,就像串行链接一样,可以从中生成浴盆曲线(使用双狄拉克统计后处理)。浴盆曲线提供了对接口BER性能的关键洞察力,无论您是在并行存储接口还是串行链路上工作,最终,这是工程师真正需要了解的内容。