Allegro Package Designer Plus SiP Layout Option

Advanced system-in-package implementation including die/BGA interface optimization

主要好处:

-

经生产和铸造验证的流程,带有多个流片

-

与PDK驱动的PVS DRC /验证的直接集成可提供图形设计者反馈,从而最大程度地减少了流片准备的过程

-

特定于WLP的高级金属创建和管理消除/减少了生态旋转

-

高性能GDSII处理缩短了流片准备的路径

-

Cadence公司®快板®包设计加上硅布局选项与Cadence的物理验证系统(PVS),可提供灵活的硅衬底和先进的晶圆级封装(WLP)的设计能力。它提供了由流程开发套件(PDK)驱动的设计规则检查(DRC),密度修改和评估,连通性验证以及掩模图稿签发。该选件适用于基于新兴的硅和基于晶圆的封装方法的设计,并且已通过台积电(TSMC)的集成扇出(InFO)工艺进行了验证。

硅布局选项与PVS结合使设计人员能够解决以下制造难题:

-

代工厂或基于硅的WLP制造商遵循的PDK,以进行DRC,验证和掩膜签名

-

PDK要求通过多种方法管理特定于硅的互连(金属)密度,以控制制造翘曲

-

使用基于硅的规则平台进行基于硅的DRC间距,制造和密度检查

-

针对包装设计结构进行了优化的高性能GDSII掩膜图稿处理和生成

-

2D和3D提取,建模和分析,以实现信号完整性(SI)和电源完整性(PI)的性能和稳定性(通过可选的Cadence Sigrity ™技术)

-

符合硅基板制造工艺规则

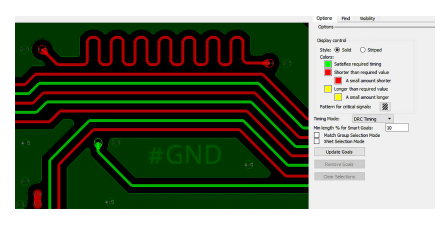

该选项已成为经过生产和铸造验证的流程的一部分,带有多个流片。与PDK驱动的PVS DRC /验证的直接集成可在Allegro Package Designer Plus画布上提供图形覆盖和表格格式的反馈,从而最大程度地减少了流片准备的过程。

注意:Cadence物理验证系统(PVS)对于硅和晶圆级设计流程是必需的,但必须单独购买。

![]()

Silicon Layout Option提供与Cadence PVS的集成,可进行基于铸造的制造规则检查