SiP Digital Architect

最大化功能密度和性能,最小化功耗

核心优势

-

简化多个高引脚数芯片在单个基板上的集成

-

支持早期设计调研,评估和权衡分析

-

与Cadence Innovus,Virtuoso®和Allegro®技术集成

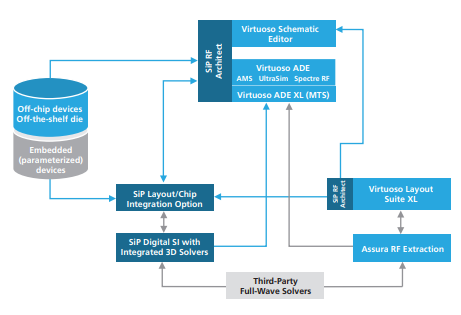

为了使您的IC封装的功能密度和性能最大化,同时又将功耗降至最低,Cadence® SiP Digital Architect管理从芯片到系统级SiP的设计流程。 SIP Digital Architect通过双向流程与Cadence Innovus™ 创新系统的数字设计数据库集成,以进行共同设计优化,并使您可以编写系统级SiP连接模式以进行可行性和验证研究。

Cadence SiP Digital Architect用户界面

随着市场需求比以往更多的功能,SiP Digital Architect使您可以快速编写系统级SiP连接模型以进行可行性和验证研究。这使您可以最大程度地提高封装的功能密度和性能,同时将功耗降至最低。 SiP Digital Architect还通过IC,基板和系统级别的优化功能执行IC I / O焊盘环/阵列协同设计。

主要功能

-

通过独特的表格和表单环境加速连接的创作和管理

-

支持快速的系统级连接捕获和“假设”场景

-

在流程中尽早解决设计折衷问题,以实现最佳性能

-

通过多级优化完成I / O垫环/阵列协同设计

-

支持双向ECO和LVS流程,以实现完整的协同设计

-

进行可行性和验证研究以优化设计

-

允许将RF和混合信号合并为分层子模块配置文件