Sigrity Advanced PI

Accelerating PDN designs

主要好处:

-

通过尽早发现布线前和布线后的潜在问题,降低成本和时间

-

通过验证AC,DC和电源纹波分析来确保可靠的电源传输

-

全面/全面地优化PDN

-

使用基于块的原理图编辑器轻松应对系统级功耗分析的挑战

为了帮助您快速验证的充分性,效率和供电网络(PDN)的稳定性,Cadence公司® Sigrity公司™高级PI允许电源完整性(PI)的专家从各个电源进行PDN验证跨多个板和封装每个汇。

Cadence的快板® PowerTree ™技术让您设置分析物理设计过程之前和验证的过程中逻辑设计阶段定义物料清单。随着物理实施的进行,可以重用PowerTree环境中捕获的设置,从而使DC和AC电源完整性分析成为每个设计阶段的按键过程。

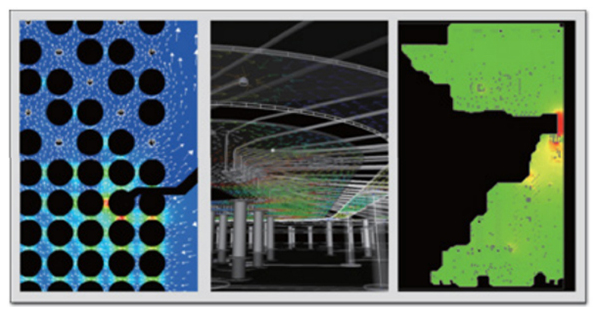

图1:准确地模拟有问题的现实世界结构,例如通过电场,引线键合和缩颈的切口

热感知直流分析

Sigrity PowerDC ™技术可为IC封装和PCB设计签核提供有效的DC分析,包括电/热协同仿真以最大程度地提高准确性。Sigrity PowerDC技术可快速查明过多的IR压降以及过大的电流密度和热点区域,以最大程度地降低设计中出现现场故障的风险。

AC分析

Sigrity OptimizePI ™技术可对电路板和IC封装进行完整的交流频率分析。它支持布局前和布局后研究,可快速找出最佳的开盖选择和放置位置,以最低的成本满足您的PDN需求。针对目标阻抗约束检查PDN阻抗曲线,以确保设计符合PDN规范。

功率纹波分析

Sigrity SPEED2000 ™技术的电源接地噪声仿真工作流程可用于I / O电源的直接时域电源/接地噪声仿真。Sigrity Advanced PI无需提取S参数模型并在SPICE仿真中使用它们,而是为PCB或IC封装提供了一种直接的时域电源完整性方法。它提供了稳定的仿真结果,否则将耗费更多时间。

Sigrity拓扑资源管理器

此通用拓扑探索功能可用于跨多个结构探索电源拓扑。通过连接芯片,封装和电路板的电源端口,您可以创建和模拟完整的源到宿连接。使用电压调节器模块(VRM)的模型可以激发使用Sigrity PowerSI ™或Cadence Clarity ™ 3D解算器创建的每种结构的PDN模型。产生的信号提供了从电源到接收器的每个关键点处PDN电压的时域视图。您可以确定PDN的任何部分在系统规格范围内供电时是否产生问题。

图2:直观的Sigrity拓扑资源管理器用户体验使

跨多个板,芯片和封装的PDN互连模型的连接变得容易,并看到了对电源稳定性的影响

跨多个板,芯片和封装的PDN互连模型的连接变得容易,并看到了对电源稳定性的影响

特征

-

使用在设计过程的示意图阶段捕获的PowerTree数据(源/接收器定义)自动设置DC仿真

-

识别难以定位,高电阻的布线瓶颈,并在成千上万的压力下找到失效的通道

-

确定是有可能减少平面层而不增加直流或热可靠性风险

-

降低新设计和后期生产产品的PDN成本

-

PDN性能的直观和交互式可视化