InFO Packaging Technology

Shorten the InFO design and verification cycle

主要好处

-

具有成本效益的系统扩展以增加系统带宽

-

降低功耗和设备尺寸

-

移动和物联网(IoT)应用的理想解决方案

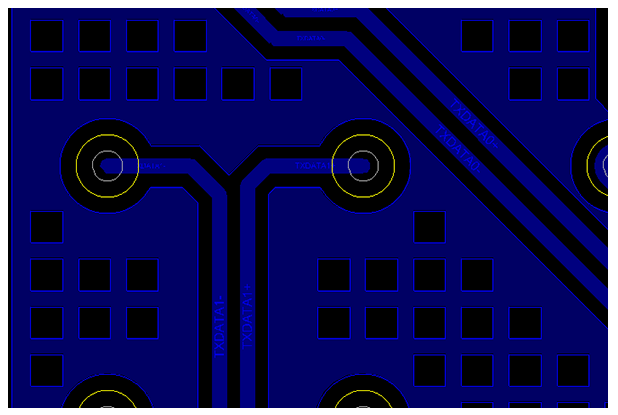

具有Cadence实现技术的InFO包装技术

使用Cadence IC级和封装设计工具的集成设计流程可提供具有InFo技术增强功能的无缝流程,从而减少总体设计周转时间

Cadence能够通过以下方式成功成功地广泛部署TSMC的集成扇出(InFO)封装技术:

Cadence能够通过以下方式成功成功地广泛部署TSMC的集成扇出(InFO)封装技术:

-

Cadence公司®物理验证系统(PVS)

-

Cadence封装系统(SiP)

-

SiP布局晶圆级芯片级封装(WLCSP)选项

-

Sigrity™IC封装分析和3D建模

-

Voltus™IC电源完整性解决方案

什么是InFO技术?

台积电的InFO技术是一种扇出,单芯片,多芯片或PoP(层叠封装)晶圆级芯片级封装技术,可提供较低的热阻,出色的RF材料特性以及极薄的层厚度,满足需要瘦设备或设备堆栈,优化性能并降低移动计算产品成本的客户的需求。

从设计师的角度来看,什么使InFO技术与众不同?

-

严格控制的局部金属密度,可提供非常非常薄的封装基板

-

台积电利用其IC工艺专业知识,工具集和流程来制造这些器件

支持技术

为了使台积电客户能够满足这些要求,Cadence现在提供了这些新的和更新的功能:

-

在SiP IC封装布局工具中,我们添加了工具,使您可以扫描,评估和修改设计每一层上的局部金属密度,以满足InFO技术的严格密度要求。

-

实现了IC封装设计工具与签收PVS DRC / LVS之间更紧密的集成,从而缩短了设计周期

-

单元级电源完整性工具,支持全面的电迁移和IR-drop(EM / IR)设计规则和要求,同时提供全芯片片上系统(SoC)电源签核准确性