Sigrity SPEED2000

Layout-based power-aware signal integrity

主要好处

-

执行时域信号完整性分析,以确认设计满足指定目标

-

通过灵活的2D和3D可视化结果(包括波形和虚拟演练)记录模拟结果

-

使用嵌入式求解器和模拟器,为基于布局的电气规则检查(ERC)提供简化的工作流

装备独特,可让您通过单个工具执行各种分析任务-Cadence®Sigrity,包括电气规则检查,互连模型提取,信号完整性(SI)和电源完整性(PI)研究以及设计阶段电磁干扰分析™SPEED2000™技术是基于布局的有限时域(FDTD)仿真工具,用于具有多个工作流程的IC封装和/或电路板分析,以指导用户完成各种分析任务。其中包括电路和传输线模拟与快速专用电磁场求解器的组合,该电磁场求解器可计算IC封装,电路板信号和平面上信号,电源和地之间的动态相互作用。

Sigrity SPEED2000技术旨在与流行的芯片/封装/板设计流程一起使用。该工具使您可以进行时域分析,以确认设计是否达到指定的目标,了解复杂的电压噪声传播(包括返回路径的不连续性),模拟同时发生的开关噪声(SSN),并帮助您确定改进的机会。Sigrity SPEED2000技术为封装和/或PCB的SI和PI提供了一个瞬态仿真环境。可以执行互连模型提取,以在纯电路模拟器(例如Cadence Sigrity SystemSI™模拟器)中支持聚焦反射(第1级)或串扰聚焦(第2级)仿真。

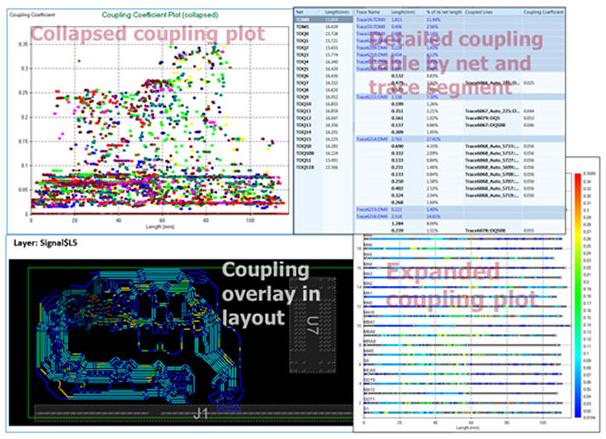

Sigrity SPEED2000 ERC工作流程的图形结果

此外,另一个流行的Sigrity SPEED2000工作流程是可识别功率的电气规则检查(ERC)。这项独特的技术扩展了经典阻抗和串扰规则检查的范围,它包括了可能会振铃的电源和接地层的估计噪声耦合。

静电放电(ESD)工作流程用于测试来自外部电源(如人与人接触或带电插入电缆)突然和意外电流流动的影响。该流程包括定义ESD喷枪模型的位置,然后观察对电路板,信号和平面的影响。瞬态电压抑制(TVS)二极管及其钳位电压峰值的能力已包含在ESD仿真中。

有无瞬态电压抑制二极管的ESD仿真差异

特征

-

全面筛选信号阻抗,串扰和返回路径不连续性的工作流程(无需模型)

-

基于仿真的SI规则检查,考虑电源平面噪声(无需模型)

-

模拟同时开关噪声(SSN)并确定改进方案

-

独特的电磁控制(EMC)仿真解决方案,支持带有非线性驱动器和接收器的设计

-

确定堆叠,平面几何形状和I / O配置变化的影响

-

观察产生噪声的位置,识别其传播方式,并确定其是否保持在目标水平内

-

单或耦合信号线的互连模型提取,以与外部电路模拟器(例如Sigrity SystemSI工具)一起使用

-

表现为Sigrity SystemSI工具的FDTD直接引擎,可进行系统级功耗感知的SI分析(无需S参数)

-

ESD工作流程可提供有关TVS二极管有效性的反馈

-

通过Cadence SiP布局,Allegro®封装设计器和 Allegro PCB设计器针对流程进行了优化

-

易于在Mentor,Zuken和Altium流程中使用,在需要多结构设计支持的地方接受混合的CAD数据库